Open Access

Open Access

ARTICLE

An Optimal DPM Based Energy-Aware Task Scheduling for Performance Enhancement in Embedded MPSoC

1 Department of Electrical Engineering, Faculty of Engineering & Technology Superior University Lahore, 54000, Pakistan

2 Department of Computer Science, Faculty of Computer Science & IT Superior University Lahore, 54000, Pakistan

3 Faculty of Computer and Information Systems, Islamic University of Madinah, Al Madinah Al Munawarah, 42351, Saudi Arabia

* Corresponding Author: Hamayun Khan. Email:

Computers, Materials & Continua 2023, 74(1), 2097-2113. https://doi.org/10.32604/cmc.2023.032999

Received 03 June 2022; Accepted 07 July 2022; Issue published 22 September 2022

Abstract

Minimizing the energy consumption to increase the life span and performance of multiprocessor system on chip (MPSoC) has become an integral chip design issue for multiprocessor systems. The performance measurement of computational systems is changing with the advancement in technology. Due to shrinking and smaller chip size power densities on-chip are increasing rapidly that increasing chip temperature in multi-core embedded technologies. The operating speed of the device decreases when power consumption reaches a threshold that causes a delay in complementary metal oxide semiconductor (CMOS) circuits because high on-chip temperature adversely affects the life span of the chip. In this paper an energy-aware dynamic power management technique based on energy aware earliest deadline first (EA-EDF) scheduling is proposed for improving the performance and reliability by reducing energy and power consumption in the system on chip (SOC). Dynamic power management (DPM) enables MPSOC to reduce power and energy consumption by adopting a suitable core configuration for task migration. Task migration avoids peak temperature values in the multi-core system. High utilization factor ( on central processing unit (CPU) core consumes more energy and increases the temperature on-chip. Our technique switches the core by migrating such task to a core that has less temperature and is in a low power state. The proposed EA-EDF scheduling technique migrates load on different cores to attain stability in temperature among multiple cores of the CPU and optimized the duration of the idle and sleep periods to enable the low-temperature core. The effectiveness of the EA-EDF approach reduces the utilization and energy consumption compared to other existing methods and works. The simulation results show the improvement in performance by optimizing 4.8% on 9%, 16%, 23% and 25% at 520 MHz operating frequency as compared to other energy-aware techniques for MPSoCs when the least number of tasks is in running state and can schedule more tasks to make an energy-efficient processor by controlling and managing the energy consumption of MPSoC.Keywords

An Embedded system is defined as a system with dedicated functionality with software utilities embedded into the hardware to perform the dedicated task. Moreover a typical embedded system can be viewed as a base hardware platform that executes applications, software and any peripheral devices connected to different ports [1]. The hardware platform consists of the processing units like CPU, graphics processing unit (GPU) communication channels and memory elements. In an operating system application-level code belongs to software implementation while power efficiency can be achieved by controlling power consumption in all the parts of the overall system [2].

In recent years embedded systems are growing phenomenally in terms of new features and applications. Mobile embedded devices now offer the integration of multimedia applications, wireless data features, internet browsing and phone. In addition, these new trends also urge managing power consumption. Further, it’s known that the use of various electronic gadgets based on MPSoCs like mobile devices has now reached approximately equal to the world’s population [3].

Designing an embedded system that gives high efficiency while dissipating low power is a major challenge for embedded system designers [4]. Power management in embedded devices is intended to improve effciency and performance in terms of energy in embedded systems. Due to advancements in computational embedded devices the execution of the task is eventually easier than ever before using multiprocessors [5,6].

An energy-aware online scheduling-based technique is used for high-performance homogeneous systems that consider both spatial and temporal gradients and their correlation with temperature evolution that enhances the system’s performance while dynamic voltage and frequency scaling (DVFS) is used for the smooth execution of tasks [7]. Scheduling is based best speed fit earliest deadline first (EDF) technique that chooses the suitable processor when the task is allocated for execution and the proposed technique doesn’t consider the fastest core. The performance and reliability of the chip are improved than that of the global earliest deadline first algorithm that considers the priority of the task while executing [8]. Migration of tasks can occur at any time with different speed processors and tasks were assigned based on deadlines those tasks that can have an early deadline can have higher priority [9].

Chip size is decreasing and the number of transistors on the chip is gradually increasing and the dimensions of the chip are getting smaller than before. The increased temperature on the chip affects the reliability and performance of the Circuit that is used in the embedded device [10,11]. Introduced a technique in which power can be reduced without changing the supply voltage by using the frequency scaling technique while the amount of overall power is the same because the energy can be decreased by Voltage scaling [12].

Most of the embedded computing circuits aim to give a maximum performance while using minimum power. Electronic circuits are viewed as a combination of different CMOS devices. CMOS devices are the basic building block of all computing systems. CMOS semiconductors uses positive channel metal-oxide-semiconductor (PMOS) or negative channel metal-oxide-semiconductor (NMOS) semiconductor PMOS. CMOS circuits consume less power as compared to other devices which are using just one type of transistor. This property makes them unique for embedded systems which are mostly used in battery-operated [13].

CMOS chips are the foundation of today’s MPSoC. A device power consumption is divided into two categories dynamic and static. Dynamic is also known as switching power and static is also known as leakage power. Leakage power became the primary power consumer in designs smaller than 90nm whereas switching is the main contribution in larger designs greater than 90nm. Both forms of power can be reduced using power reduction [14,15]. Energy-efficient scheduling techniques for multi-processor are introduced with an EDF scheduling algorithm that extends the battery life. EDF can be extensively used for both offline and online scheduling. Offline scheduling is inflexible and has deterministic timing behavior for a deterministic system. In offline scheduling complexity is not important and have low run-time overhead. In online scheduling the parameters of each task are known when the job is released and is widely used for unpredictable workloads [16].

For many years the primary factor in CMOS circuits has been dynamic power dissipation which happens as a result of transistor switching

where

where

The main contributions of this paper elaborates and mathematical prove the concept of energy efficiency using scheduling. A peak-Energy and power-aware energy management task scheduling scheme that is conducted at offline phase using our proposed EA-EDF scheduling algorithm for optimizing the energy.

In this paper mainly proposing task switching techcnique using EDF scheduling mechanism to manage the energy and peak power consumption and achieve further reduction in energy/peak in the MPSoC.

CPUs with more transistors are now available due to rapid development in semiconductor technology [20]. High-end CPUs are widely used in real-time embedded systems however total chip power consumption in CMOS is considerably increasing with rapid growth in technology can be calculated using Eq. (4) mentioned below.

The static power consumption

where f represents frequency V represents supply voltage and C denotes capacitive load and K is the proportionality constant. The DVFS approach uses the slack time that arises when scheduling tasks to adjust the voltage and frequency of the CMOS chip [22]. DPM technique is reducing energy losses when the slack time arrives reducing energy usage by transitioning to a low power state. Energy overhead is imposed due to break-even time increasing gradually. There will be a loss as a result of the state transfer [23,24]. The below Eq. (6) determines the break-even time (BET) sleep.

Recognizing the significance of low power and energy consumption and thermal concerns in multiprocessor systems. Several strategies for managing real-time scheduling while addressing thermal limits were previously presented to regulate peak temperature, energy and performance. The majority of them use DPM and DVFS [25]. EDF scheduling algorithm can have dynamic priorities. The scheduler can select those tasks that are in the ready queue whose deadlines are coming next and are very useful for the uni-processor. The utilization factor of the process is less than is approximately equal to 1. In hard real-time systems, these jobs are schedulable for a preemptable task and can attain 100% utilization for a central processing unit. Using the EDF scheduling technique the utilization of the CPU improves because of the implication of dynamic priority. The priority of selecting each task depends on the fixed deadlines [26,27].

2.1 Energy Monitoring Phase in MPSOCs

In this section the mechanism for energy monitoring is discussed using Intel PXA270 MPSoC. Intel PXA270 processor has a variety of operating modes. For optimization of energy, there are three modes active, idle and sleep. Power modes are drastically different in terms of their capabilities including the transition time according to the energy required to perform. The power consumption for various states of Intel PXA270 is Mined from the datasheet of the Intel® PXA270 Processor Electrical, Mechanical and Thermal Specification used for enabling the low-power mode [28]. Several energy-saving features are built into the CPU. The four main energy-saving modes are the ones that stand out the most. Tab. 2 demonstrates the consumption of the Intel PXA270 MPSoC on various power modes as well as the nominal current consumption. In the STORM Simulator’s XML specification input a tag named CPU is used to represent this type of processor in simulation [29].

2.2 Higher Power Consumption Causes Thermal Problems

This section elaborates the issues causes due to high task utilization that mainly leads to higher possible power consumption. Higher power consumption on-chip causes higher temperature and higher resistance that lower the possible speed of MPSoC. Lowering the temperature on the chip reduces the resistance lowers the power consumption and causes a higher possible speed. Fig. 1 illustrates the effects of high-power dissipation that produces heat because of (energy consumption/loss or waste) as an undesirable derivative of its primary action illustrates that chip power dissipation is increasing as the processing capabilities of MPSoCs grow resulting in a large increase in chip temperature. As the chip size is shrinking and the numbers of transistors are increasing per unit area on the chip this leads to more power consumption, complexity and increases in the temperature of the chip. The designers of MPSoCs face significant difficulty in achieving the maximum performance system with high utilization [30].

Figure 1: Effects of high power dissipation produce thermal upsurge

Power consumption, scheduling and switching of tasks from one core to another core is one of the major issues in today’s MPSoC. Given a system model having various CPUs are represented by m and a periodic task contains the power model of MPSoC and a task model that normally schedules the workload on each core individually. The optimal solution includes a task migration and core switching technique to reduce the energy consumption of the system.

Consider a system having a periodic task set

3.1 Proposed EA-EDF & Task Model

This section elaborates the methodology that is opted for the proposed scheduling technique and task model. The proposed system model gives a comprehensive description of the elements that are involved in conducting experiments. The major components include a task generator, simulator, core configurations and scheduling algorithm where users can create random task sets in xml.txt file that contains different parameters. The parameters in the extensible markup language (XML) file are used as an input for the simulation tool including period, activation time, deadline, worst-case execution time (WCET), priority and best-case execution time (BCET). Task set generator contains random task sets that are used to create the workloads under different constraints as well as the no of CPU cores set by the user in XML according to the application provided to STORM as an input. The scheduler can have a set of ready tasks and simulate the input file according to the scheduling policy by considering task migration and task balancing according to the configuration policy for cores that are developed in the proposed algorithm producing the power profiles of the individual core according to the given set of parameters in XML.

Fig. 2 illustrates the proposed EA-EDF scheduler that organizes resources to meet the deadlines and forecast the utilization factor. The power module is integrated as part of the scheduling policy. The STORM Simulator considers each processor to be an execution unit that runs the task. As a result the scheduling method determines the frequency and power states (idle, waiting). To schedule the n tasks, the EA-EDF scheduling approach employs the task scheduling policy and allocates a single processor for each subset after the scheduler assigns work. Task migration allows the scheduler to place some high-power running cores of processors in idle mode and enable other processors that were previously idle. If a job with a higher priority is waiting in the ready task queue the present process is preempted and placed in idle mode. The work in the ready task queue with the shortest deadline receives the highest priority if two jobs have the same priority at time t. The Input XML file can have all the information about the complete simulation duration for the execution of experiments, hardware resources that are required according to the load, architecture for task set and scheduling algorithm. Simulations will be considered using the Intel PXA270 multiprocessor which is preferable because the processor has an intelligent power saving mechanism.

Figure 2: Proposed EA-EDF scheduling model

We adopt a classic real-time task model for this by considering an Intel PXA270 MPSoC platform denoted by

As our proposed scheduler is dynamic so priority will remain fixed for all tasks and the task can be instantiated an infinite number of times. The task set contains n periodic task

This section elaborates the power model that calculates the static and dynamic consumption of power in CMOS circuits. Eq. (7) illustrates the dynamic power consumption

where V is the required supply voltage, while the frequency component is represented as f while

where

Eq. (10) represents the consumption of energy over a period [

The consumption of energy over workload

Energy consumption of cores of the MPSoC is represented as static power and dynamic power. As long as the CPU is in on state static power is consumed while dynamic power is consumed during computation times as shown in Eq. (12).

Static power was approximately negligible in earlier processors: For n no of transistors the parameter that is considered as design-dependent is represented as

where

The original goal of EA-EDF and DPM is to reduce the energy consumption by switching the processor to low power state. Generally, in MPSoC consumption of energy gives a higher hierarchical view of energy saving so it is obvious to measure the energy. However, the impact of a EA-EDF scheduling algorithm and the workload is investigated on different components of the hardware mainly CPU because its a major energy-consuming component. The energy consumption of the CPU decreases with an increase in sampling periods of a system with tasks

Figure 3: Normalized CPU energy consumption using proposed EDF scheduling model

3.3 Core Selection and Task Scheduling Classification

In this section the selection of core is elaborated as the operational frequency and supply voltage of a CMOS device determine its power consumption as shown in Eq. (17) is representing the association between CPU power consumption and supply voltage:

CPU requires higher supply voltage while working at a higher frequency as compared to processor operating at a lower frequency stated in Eq. (18). As a result CPUs have the higher capacity by supplying the higher voltage.

In CMOS transistor f is the frequency where

Scheduling and switching of

We are considering configurations for octa-core multiprocessor in which the migration of task depend on the utilization factor. There are a total of eight possible configurations in a processor to run different tasks and the coolest core configuration can have the highest priority to be selected first. Tasks that are in a ready state are placed in the ready task queue. The core configurations are defined against the range of

• Configuration 1

• Configuration 2

• Configuration 3

• Configuration 4

• Configuration 5

• Configuration 6

• Configuration 7

• Configuration 8

Demand bound (

Eq. (19) represents the demand bound for n periodic task set

We are using EA-EDF to map the tasks on different cores while the configuration is defined according to the range of utilization factors. The counter used in the algorithm calculates how many times a configuration is selected due to which it is easy to avoid the repetitions of the same configuration again and again. Spatial gradients are also avoided due to the counter because when a core has not been selected the value of the Counter is zero and once a Configuration is selected its counter for the running duration is increases unless it reaches the threshold utilization and tasks start migrated to other configuration.

Section 4 elaborates the experimental technique using the STORM Simulator. Additional support is provided by considering the hardware architecture of Intel PXA-270 MPSoC with DPM capabilities. Core configurations are selected according to the task load and utilization factor e.g., we assume that the power model is the same for all the cores. In the test scenarios we have adopted the power model of the Intel PXA270 processor for each core because Intel PXA270 supports 7 Power-states (from 13 to 624 MHz) and 3 major C-states including active, idle and sleep. We have performed various experimental tests. In the test scenario, we applied energy-efficient EDF as a real-time task scheduler on each configuration of the core by considering the synthetic task set. We have evaluated the behavior of our proposed algorithm in which all the tasks run until the

Figure 4: Proposed experimental model for energy-efficient scheduling

The features of the task set include the software architecture, start time and worst-case execution time, period. Priority, deadline, hardware architecture no of cores, proposed scheduling algorithm that is added into XML file. This XML File is then given to the simulator STORM where the scheduling policy is already implemented after the execution of the new scheduling-based task migration policy on Eclipse JAVA Neon 64bit using the storm jar file the simulator can produce various Power profiles, Energy-efficient results according to the load utilization factor and CPU load curves, CPU memory consumption, CPU energy consumption for Individual cores using both hardware & software architecture of the processor model for all type of hardware configurations already mentioned in an XML file as input to the simulator Scheduling technique for Multicore Intel PXA-270 MPSoC. Intel PXA-270 processor’s power model is used for each core in the test scenarios because the Intel-PXA270 offers seven power states. We tested the behavior of our proposed method by running all tasks

Fig. 4. Illustrates the proposed experimental model that assess the reliability using the mentioned experimental setup. The proposed scheduling technique calculates the energy and power and switches the tasks on the core based on their utilization factor. In our experiments all hardware parameters are used from the intel PXA270 processor various configurations are used that are depending on the utilization factor of the core.

The utilization of the processor reaches near to threshold. The tasks start migrating to the core that is physically distant from the core with high power consumption due to high utilization of task and temperature for attaining better performance and avoiding delay in the execution process. Selection of core configuration is based on the stae of the core. Due to high load on CPU tasks are scheduled and migrated to the coolest core that is in sleep mode and is prior shifted to idle mode before the migration of the task.

Tab. 2 represents various power consumption states of Intel PXA-270 over multiple operating frequencies respectively by considering various states of running, idle and sleep. It also represents the current of the Intel PXA-270 CPU on various frequencies. All hardware characteristics from the Intel-PXA270 processor are employed in our tests to achieve better performance and minimize delays in the execution process. The proposed EA-EDF migrates tasks to a core that is physically away from the core with the highest power consumption and temperature. This section presents the evaluation of our improved energy-efficient scheduling algorithm for the optimization of energy and power. The proposed energy aware-EDF-based scheduler gives improved results and more energy optimization as compared to previous techniques. The Intel PXA-270 MPSoC is used to measure CPU energy usage. According to the proposed algorithm the job with the earliest scheduling deadline is prioritized When the periodic task set is examined the strategy works well that’s why the context switch is valuable.

5 Simulation Results & Analysis

The CPU energy consumption is measured concerning Intel PXA-270 MPSoC. The proposed Algorithm selects the task having the earliest scheduling deadline selected on priority. The technique works efficiently when a periodic task set is considered that’s why the value of the context switches. Simulation shows that STORM Simulator provides performance criteria that are similar to the real platform values by considering the same experimental parameters such as deadlines and energy consumption. The comparison of energy consumption at various utilization factors

Figure 5: Comparison of energy consumption

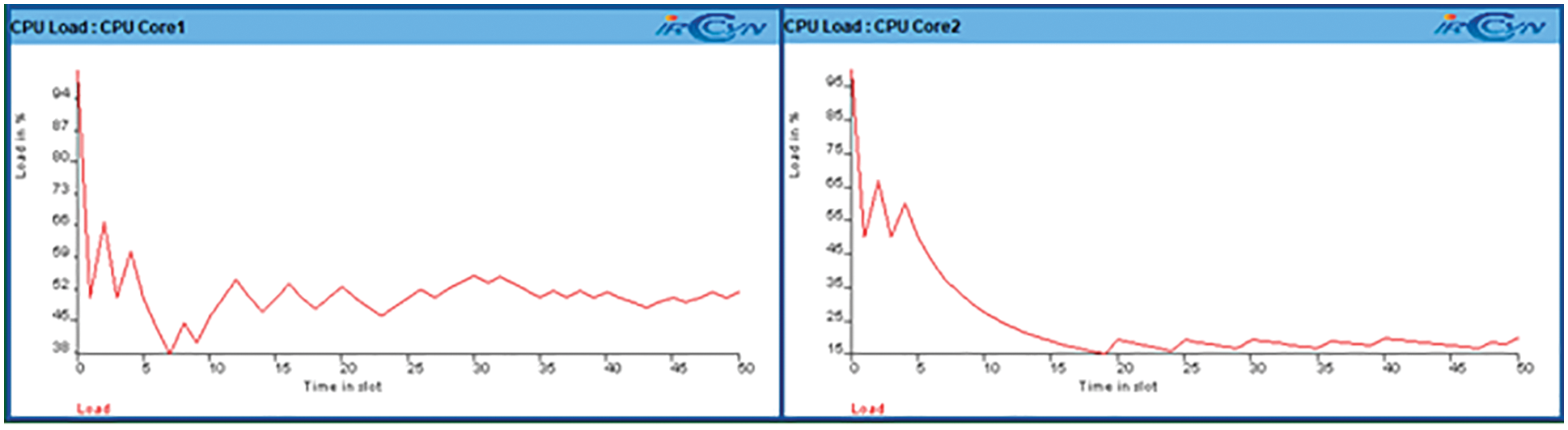

Fig. 6 represents the impact of CPU load on individual core over time due to increasing the number of periodic tasks with implicit deadlines are reducing the energy and power consumption using the proposed approach. It also illustrates that by increasing the task load on the CPU the power denisties are increasing rapidly but due to EA-EDF scheduler the tasks on core 1 switches to core 2 and dissipate less energy as compare to core1.

Figure 6: CPU load curve at CPU cores1 & cores2 under

Tab. 4 represents the comparison of proposed EA-EDF at various workloads

This research paper targets energy-efficient multiprocessor scheduling problems over τi ∈

Acknowledgement: The researchers wish to extend their sincere gratitude to the Deanship of Scientific Research at the Islamic University of Madinah for the support provided to the Post-Publishing Program1.

Funding Statement: The authors received no specific funding for this study.

Conflicts of Interest: The authors declare that they have no conflicts of interest to report regarding the present study.

References

1. H. Wang, X. Guo, S. X. D. Tan, C. Zhang and H. Tang, “Leakage-aware predictive thermal management for multicore systems using echo state network,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 39, no. 7, pp. 1400–1413, 2019. [Google Scholar]

2. S. Z. Sheikh and M. A. Pasha, “A dynamic cache-partition schedulability analysis for partitioned scheduling on multicore real-time systems,” IEEE Letters of The Computer Society, vol. 3, no. 2, pp. 46–49, 2020. [Google Scholar]

3. M. Shan and O. Khan, “Accelerating concurrent priority scheduling using adaptive in-hardware task distribution in multicores,” IEEE Computer Architecture Letters, vol. 20, no. 1, pp. 17–21, 2020. [Google Scholar]

4. J. Feliu, J. Sahuquillo and S. Petit, “Thread isolation to improve symbiotic scheduling on smt multicore processors,” IEEE Transactions on Parallel and Distributed Systems, vol. 31, no. 2, pp. 359–373, 2019. [Google Scholar]

5. D. Somdip, S. Isuwa, S. Saha, A. K. Singh and K. M. Maier, “CPU-GPU-memory DVFS for power-efficient MPSoC in mobile cyber physical systems,” Future Internet, vol. 14, no. 3, pp. 91–103, 2022. [Google Scholar]

6. R. A.prasath, J. Alzubi and M. Ramachandran, “A high performance scalable fuzzy based modified asymmetric heterogene multiprocessor system on vhip (AHt-MPSOC) reconfigurable architecture,” Journal of Intelligent & Fuzzy Systems, vol. 42, no. 2, pp. 647–658, 2022. [Google Scholar]

7. T. Yu, R. Zhong, V. Janjic, P. Petoumenos and J. Zhai, “Collaborative heterogeneity-aware os scheduler for asymmetric multicore processors,” IEEE Transactions on Parallel and Distributed Systems, vol. 32, no. 5, pp. 1224–1237, 2020. [Google Scholar]

8. P. Fruehauf, A. Munding, K. Pressel, P. Schwarz and M. Vogt, “Chip-package-board reliability of system-in-package using laminate chip embedding technology based on cu leadframe,” IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 10, no. 1, pp. 44–56, 2019. [Google Scholar]

9. W. Alberto, E. Kim, R. Renato and R. Andre, “Power consumption analysis in static cmosgates,” in 26th Symp. on Integrated Circuits and Systems Design (SBCCI), Curitiba, Brazil, pp. 1–6, 2013. [Google Scholar]

10. G. Khadidja, B. M. Kamel, B. Aboue and A. K. Singh, “A new efficient multi-task applications mapping for three-dimensional network-on-chip based MPSoC,” Concurrency and Computation Practice and Experience 33, vol. 33, no. 10, pp. 1–20, 2021. [Google Scholar]

11. R. A. Prasath, J. A. Alzubi and M. Ramachandran, “A high performance scalable fuzzy based modified asymmetric heterogene multiprocessor system on chip (AHt-MPSOC) reconfigurable architecture,” Journal of Intelligent & Fuzzy Systems, vol. 42, no. 2, pp. 647–658, 2022. [Google Scholar]

12. L. Chenyun, X. Li, C. Tang and Q. Wu, “A power management circuit compatible with Ti smart reflex and xilinx ultrascale MPSoC dual voltage mechanism,” in 10th Int. Conf. on Computing and Pattern Recognition, Shanghai, China, pp. 357–362, 2021. [Google Scholar]

13. E. Jiang, L. Wang and J. Wang, “Decomposition-based multi-objective optimization for energy-aware distributed hybrid flow shop scheduling with multiprocessor tasks,” Tsinghua Science and Technology, vol. 26, no. 5, pp. 646–663, 2021. [Google Scholar]

14. C. Y. Liang, S. Liu, E. Y. Chung and J. L. Gaudiot, “An energy and performance efficient dvfs scheme for irregular parallel divide-and-conquer algorithms on the intel SCC,” IEEE Computer Architecture Letters, vol. 13, no. 1, pp. 13–16, 2013. [Google Scholar]

15. A. Italo, O. Antonio, T. Barros, I. M. Sardina, C. P. Bianchini et al., “Distributed-memory load balancing with cyclic token-based work-stealing applied to reverse time migration,” IEEE Access, vol. 7, no. 1, pp. 128419–128430, 2019. [Google Scholar]

16. K. Baital and A. Chakrabarti, “Dynamic scheduling of real-time tasks in heterogeneous multicore systems,” IEEE Embedded Systems Letters, vol. 11, no. 1, pp. 29–32, 2018. [Google Scholar]

17. K. Huang, K. Wang, D. Zheng, X. Jiang, X. Zhang et al., “Expected energy optimization for real-time multiprocessor socs running periodic tasks with uncertain execution time,” IEEE Transactions on Sustainable Computing, vol. 6, no. 3, pp. 398–411, 2018. [Google Scholar]

18. J. Haris, M. Shafique, J. Henkel and S. Parameswaran, “System-level application-aware dynamic power management in adaptive pipelined MPSoCs for multimedia,” in IEEE/ACM Int. Conf. on Computer-Aided Design (ICCAD), Washington, D.C, Country, pp. 616–623, 2011. [Google Scholar]

19. K. George and D. Pnevmatikatos, “Dynamic power and thermal management of NOC-based heterogeneous MPSoCS,” ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 7, no. 1, pp. 1–26, 2014. [Google Scholar]

20. S. E. Abdellaoui and Y. Fakhri, “Power management strategies in energy-harvesting wireless sensor networks,” International Journal of Communication Networks and Information Security, vol. 13, no. 1, pp. 136–142, 2021. [Google Scholar]

21. Y. Yongkun, Y. Zhao and Y. Liu, “Recent progress in organic field-effect transistor-based integrated circuits,” Journal of Polymer Science, vol. 60, no. 3, pp. 311–327, 2022. [Google Scholar]

22. X. Zhang, X. Chen, W. Sun and X. Z. He, “Vehicle re-odentification model based on optimized denseNet121 with joint Loss,” Computers, Materials & Continua, vol. 67, no. 3, pp. 3933–3948, 2021. [Google Scholar]

23. B. James, V. Tenentes, B. M. AlHashimi and G. V. Merrett, “Online tuning of dynamic power management for efficient execution of interactive workloads,” in IEEE/ACM Int. Symp. on Low Power Electronics and Design (ISLPED), Boston, United States, pp. 1–6, 2017. [Google Scholar]

24. B. G. Maryam, “MPSoC based dynamic power management in wireless sensor networks,” in Int. Conf. on Information Communication and Embedded Systems, Chennai, India, pp. 1–6, 2014. [Google Scholar]

25. P. Bogdan, R. Marculescu and S. Jain, “Dynamic power management for multidomain system-on-chip platforms: An optimal control approach,” ACM Transactions on Design Automation of Electronic Systems (TODAES), vol. 18, no. 4, pp. 1–20, 2013. [Google Scholar]

26. W. Yankai, S. Wang, B. Yang, L. Zhu and F. Liu, “Big data driven hierarchical digital twin predictive remanufacturing paradigm: Architecture, control mechanism, application scenario and benefits,” Journal of Cleaner Production, vol. 248, no. 1, pp. 119–299, 2020. [Google Scholar]

27. Z. Xiaorui, W. Zhang, W. Sun, H. Wu, A. Song et al., “A real-time cutting model based on finite element and order reduction,” Computer Systems Science and Engineering, vol. 43, no. 1, pp. 1–15, 2022. [Google Scholar]

28. U. Richard, A. M. Deplanche and Y. Trinquet, “Storm a simulation tool for real-time multiprocessor scheduling evaluation,” in IEEE 15th Conf. on Emerging Technologies & Factory Automation (ETFA), Bilbao, Spain, pp. 1–8, 2010. [Google Scholar]

29. C. A. Kivilcim, T. S. Rosing, K. Mihic and Y. Leblebici, “Analysis and optimization of MPSoC reliability,” Journal of Low Power Electronics, vol. 2, no. 1, pp. 56–69, 2006. [Google Scholar]

30. P. M. Kumar and R. Nagendra, “Simulation of real time multiprocessor static scheduling algorithms,” i-Manager’s Journal on Embedded Systems, vol. 7, no. 1, pp. 30, 2018. [Google Scholar]

Cite This Article

Copyright © 2023 The Author(s). Published by Tech Science Press.

Copyright © 2023 The Author(s). Published by Tech Science Press.This work is licensed under a Creative Commons Attribution 4.0 International License , which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Submit a Paper

Submit a Paper Propose a Special lssue

Propose a Special lssue View Full Text

View Full Text Download PDF

Download PDF Downloads

Downloads

Citation Tools

Citation Tools